## ELECTRONIC DESIGN AUTOMATION TOOLS: FUTURE OPPORTUNITIES FOR BEGINNERS

Mr. Priyank Bhupendrakumar Modi L D College of Engineering, Ahmedabad Mr. Kinnar G. Vaghela L D College of Engineering, Ahmedabad

#### **ABSTRACT:**

EDA tools transform the learning, experiment, and assessment environment of the electronics industry. In this review paper, we characterize the experimental analysis of EDA tools, as the electronics industry evolved, the insolubility of the circuit rises and the growth of integrated circuits accelerated. The main focus of this paper is providing many EDA tools for different platforms. We present an experimental analysis of the robust parameterization of Electronic Design Automation (EDA) tools concerning a different understanding of essential aspects offered to beginners. However, we display that most of the studied tools are critically useful here. The results of the EDA tool indicate that experiments conducted to evaluate the performance of the EDA tool should consider such behavior.

# **KEYWORDS:** EDA Tool, Embedded, Design Process, Layout tool, Simulation, PCB Layout, Analog-Digital design, Patent trend

#### **1. INTRODUCTION:**

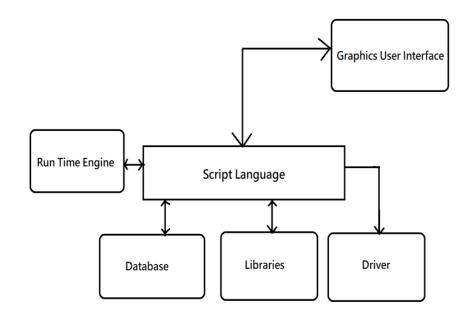

According to experts, Electronic designing is one of the complex tasks for designers or engineers. A prototype created using hardware involves high costing or also at times high failure rates. The higher complexity of designing any system without logic or idea is not be considered at all. EDA is a tool that is defined help to engineers or students or electronic beginners to design any system. EDA is a term categorized in the software tool. Normally made of basic prototype concept as hardware form is very expensive and time wasting thing as well we face failure in most of the cases. Today it is possible to simulate the design of anything from a normal RC circuit to a microprocessor chip by using the proper methodology of EDA tools. It is an approach where it is used to simulate the circuit and allow proper electronics design methods. Software algorithms and applications are required for the design of complex next-generation semiconductor devices, electronic circuits, and embedded systems for future requirements and opportunities. Due to the elevated anfractuosities of current designs, In this paper, we will present an experimental evaluation of electronic design automation devices, which use precise logic synthesis and optimization algorithms, to illustrate that the tools are much more helpful. Today it is possible to simulate the design of an electronic blueprint using a computer and proper software tools. The use of software tools for the design and simulation of electronic circuits is one type of approach we can say is EDA. The EDA tools offer the design and development of electronic design with proper methodology, we can create a design, simulate it. It provides flexibility and reduces the workload of engineers or designers. As a result, we hope that this work will be useful for other beginners in identifying the strengths and weaknesses of different EDA tools.

(Fig 1 : EDA Tool basic understanding)

### 2. NECESSARILY OF EDA TOOL:

At that time, there was no EDA. There was only engineering by hand. Before EDA came into the scene, developing basic circuits to any integrated circuit was very difficult. The procedure takes a considerable amount of time and leads to several failures with various schematic errors at the end. The complexity of electronics shows us the necessity of automation. Currently, many EDA tools are available for design in accordance with an individual's intellectual property. The designing of electronics systems and their circuits has many deep histories. EDA was named for the first time in the 1960s when researchers created the CAD (Computer-Aided Design) tool for supporting engineers in the analysis and layout of circuits. In such a way we can reduce the amount of work, the duration of time, and the difficulty of analogical problems. In the 1970s SPICE, was an open source analog electronic circuit simulator developed by the University of California. At the ending of the 2000s, the need for EDA is increased due to its complexity and time reduction advantages. Today, there are many options available in the market when it comes to EDA tools. A few of them are open-source tools, but others require a confidential key. User applications determine how it works. The electronics industry is reevaluating engineering design tools.

There are basic features in tools:

- 1. Automated system that allows for automatic invocation and control of other systems through callbacks, for instance, so that they are notified of interacting events.

- 2. Using user requirements to determine whether additional computation is necessary and whether it can be deferred.

- 3. Other tools get notified when changes are made so they can make any required updates.

- 4. Data reversibility allows us to easily undo changes, save, and restore data.

A manufacturing facility uses a combination of digital and analog architectures to create an electronic chip or circuit. EDA tools have several advantages, including saving time spent developing complex circuits, eliminating manufacturing errors, lowering manufacturing costs, optimizing design, and ease of use.

## 3. DIFFERENT WAYS FOR CHOICE EDA TOOL:

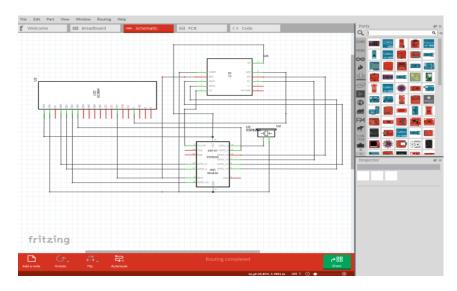

Before the revolution of technology or tools, to design a circuit, Circuits were traditionally drawn by hand or with geometric software. Circuit designers began utilizing software to automate the design process in 1970. The majority of EDA tools follow a flow diagram. There are two types of design flow: digital design and analog design. In digital design, the circuit is described with a hardware description language, and then simulated, synthesized, routed, and post-routed. A circuit is captured in analog design, there are then simulations, physical designs, layout extractions, and post-layout simulations. When producing electronics circuits or chips, a production facility uses digital and analog layouts combined. To design any devices or circuitry passes through many stages, from drawing an idea to determining the final layout. There are many lots of EDA tools available just for designing circuit boards and simulating any circuit. For example, OrCAD, Eagle, Fritzing, etc. If any designer wants to design an integrated circuit or chip there are several EDA tools available like Xilinx, Questa, Mentor graphics, Maxplus2, SPICE, etc. if we are going to make any embedded system there is Proteus Design Suite and many more EDA tools are available.

The EDA tools are categorized into three types:

- A. Design suit Tools

- B. Simulation And Layout Tools

- C. Verification and Q&A Tools

#### **3.1 Design Suit Tools:**

The starting of EDA tools as an industry happened in 1981, when Hewlett-Packard, Tektronix, and Intel started to use EDA tools internally. Several companies were founded at this time, such as Daisy Systems, Mentor Graphics, and Valid Logic Systems. It is a design process tool that is engineer required to design any circuit. For engineers and beginners, it is very time-consuming to design a circuit or system. For saving time and power we can design a user-defined application. It is prepared for designing simple circuits to schematic and PCB boards. With the help of the Design suit tool schematic designer have extensive components libraries, options to create their circuits and PCBs, they create their netlists as well as easily find and detect the error in the schematic.

(Image of 3.1: Microcontroller interfacing using the fritzing tool)

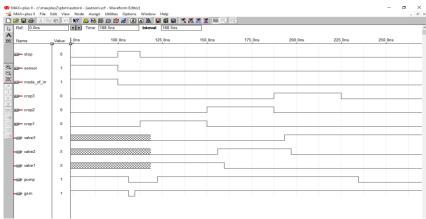

#### **3.2 Simulation and Layout Tools:**

There was a hardware description language created in 1981 by the name of VHDL, followed by another one developed in 1986, called Verilog, which is similarly named. In a few years, back-ends for doing logic synthesis emerged along with simulators to support these languages. It is a functional verification tool of EDA. It checks the functionality of the designed circuit or system as user-defined. Sometimes it is a free and open-source EDA tool means a package of software we can use with a free license. In simulation there are mainly two major categories are included one is logical and the other one is timing-based. Simulation tools verify logic design VHDL simulation, Gate circuit design, any kind of automation tools. Where a timing-based simulator uses for multiple applications of design. Normally maintaining all features of EDA tools has been categorized. There are lots of free EDA tools with open source. Some of them are used as physical design tools.

| use ieee.std_logic_1164.all;<br>entity Simulator: Timing Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                       | -        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| port(<br>Simulation Input: autoirri.scf<br>Simulation Time: 1.0us<br>Start Time: [0.0ns End Time: 1.0us]<br>Use Device Oscillation [0.0ns]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                       | _        |

| erd au  o  Southant  o  Southan |                                                                                                                                                       | _        |

| archit<br>begin<br>process(mode_of_irr,sensor,crop1,crop2,crop3,stop)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MAX+plus II - Simulator X                                                                                                                             | _        |

| begin<br>if mode_of_irr-'1' and stop-'0' then<br>irrigation through sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Project simulation was successful<br>cruit stabilized at 997.1nc;<br>Simulation ereded at 1.0us<br>Simulation coverage: 92%<br>0 errors<br>0 warnings | _        |

| if sensor='1' then<br>pump<='1';<br>gsn<='1';messeage sends to operator about pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ок                                                                                                                                                    | _        |

| else<br>pump<='0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                       | <b>_</b> |

| ine 1 Col 1 INS (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                       | <u> </u> |

(Image of 3.2: VHDL simulation on Maxplus 2 tool)

### 3.3 Verification and Q&A Tools:

With the introduction of VLSI (Very Large Scale Integration) in 1980, programming languages entered the story to simplify the compilation of electronic designs. Later on, simulation and verification tools were developed to design more complex integrated circuits. Electronic engineers, designers, and students can design the logical representation of circuits, chipset, a microprocessor device, or any PCB board converting into a physical representation that allows for the manufacturing of that thing. After Completion of any simulation work of project designer can check the quality and analysis test by using EDA tools. Once creating the simulation or designing any chip or circuit user or designer can create a layout printing on a physical board. Sometimes procedure of layout is manual, but most steps for PCB layout creation are automatic in nowadays EDA tools. In VLSI, some functionality such as HDL turned into gate-level representation. The academic community makes wide use of EDA tools such as KiCAD, Logisim, OrCAD, PSPICE, NGSPICE, and many more for VLSI design.

(Image of 3.3: Output waveform of HDL Entity on Maxplus 2 tool)

## 4. BENEFITS OF EDA TOOLS:

EDA tool helps students, engineers, and designers to manage high complexity in designing and simulation any project. A designer can explore different things in design approaches. EDA tools also help industries. Normally some EDA tools are likely to open and free source software where it can be used with the free license. EDA tools have much more features and most of them can fill up maximum demands of users or designers. EDA tools help to achieve more complex chips or circuits at a lower cost in a shorter time. It also helps layout designers to place millions of transistors on a single chip as well as micro semiconductors on a single board. EDA tools also check physical as well as electrical design rules for all semiconductors. EDA has a special program that allows the designers to estimate the value of system performance and life cycle. Normally every product from electronics toys to satellites all designers are use EDA tools and services. Electronics has become even more complex, as well EDA is more important worldwide in the educational sector, in industry, as well as for the world economy.

| COMPONENT KINDS                 | QUCS         | LTspice 1V   | eSim (OSCAD) |  |  |

|---------------------------------|--------------|--------------|--------------|--|--|

| Components with passive         | ,            |              | ,            |  |  |

| characteristics (e.g.,          | $\checkmark$ |              |              |  |  |

| Register, capacitor,            |              |              |              |  |  |

| inductor, etc.)                 |              |              |              |  |  |

| Devices that are active         |              |              |              |  |  |

| (such as transistors, diodes,   | $\checkmark$ |              |              |  |  |

| and integrated circuits)        |              |              |              |  |  |

| Power Sources (Voltage          |              |              |              |  |  |

| and Current)                    | $\checkmark$ |              |              |  |  |

| COMPONENTS OF THE DIGITAL WORLD |              |              |              |  |  |

| Gates like AND, OR, XOR,        |              |              |              |  |  |

| NOT                             | $\checkmark$ | $\checkmark$ |              |  |  |

| Gates like NAND, NOR,           | $\checkmark$ | Х            |              |  |  |

| XNOR                            |              |              |              |  |  |

| SR, D Flip flop                 |              | $\checkmark$ |              |  |  |

| JK, T Flipflop                  |              | Х            |              |  |  |

| VHDL Files                      |              | Х            | Х            |  |  |

| VERILOG Files                   |              | Х            | Х            |  |  |

| ANATOMY TYPE                    |              |              |              |  |  |

| Transient                       |              |              |              |  |  |

#### 4.1 Table 1 of comparison of EDA tools:

| AC                           | $\checkmark$        | $\checkmark$     |              |

|------------------------------|---------------------|------------------|--------------|

| DC                           |                     | $\checkmark$     |              |

| Digital                      | $\checkmark$        | $\checkmark$     | $\checkmark$ |

| Equilibrium in harmonics     | $\checkmark$        | X                | X            |

| Parameter S                  |                     | $\checkmark$     | X            |

| Sweep of parameters          |                     | Х                | X            |

| Noise                        |                     | $\checkmark$     | X            |

| Enhancement                  |                     | X                | X            |

| Simulation of subcircuits    |                     |                  |              |

|                              | AL                  | SO               | •            |

| Is it compatible with        |                     | $\checkmark$     | X            |

| Windows?                     |                     |                  |              |

| Tools available for free     |                     | Х                |              |

| Can we use another           | LINUX, SOLARIS, MAC | FOR LINUX WINE   | LINUX        |

| platform?                    |                     | REQUIRED         |              |

| Format for spice netlists    | X                   |                  |              |

| Design of PCBs               | X                   | X                |              |

| Web app                      | X                   | X                |              |

| Each step of the circuit     | X                   | X                |              |

| equation                     |                     |                  |              |

| Check erc                    | X                   | Х                |              |

| Bom (bills of material)      | X                   |                  |              |

| It is possible to export the | $\checkmark$        |                  |              |

| simulated data               |                     |                  |              |

|                              |                     | C 1 1 1 1 0010 D | 1.0 ( [0]    |

Source: Electronic Design Automation Tool: a Comparative Study, March 2019, ResearchGate [2]

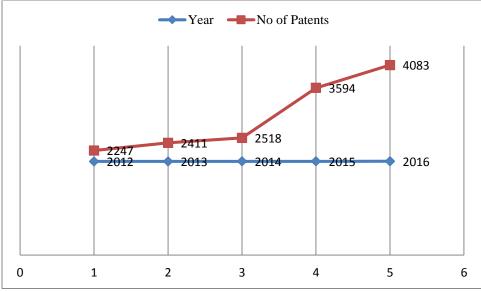

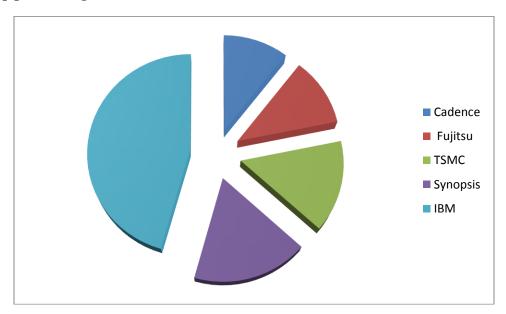

We can observe from the patent publication trend from the graph that the EDA tools industry is also growing rapidly all around. Among the major players, we see IBM and Cadence as well as Synopsis, Fujitsu, and TSMC.

#### Graph 1: Trends in EDA, patent publication

Source: Analysis data based on Legal Advantage's blog [6]

Graph 2: Top patent assignees in the EDA domain

Source: Analysis data based on Legal Advantage's blog [6]

### 5. CONCLUSION:

We have compared EDA tools using different parameters which are useful for beginners and students. Design and testing analog circuits can be done using tools with a proper GUI which are easily understood and easily used by students, engineers, and faculty members. From this paper, we can conclude that it is a good option to use testing, simulation techniques to design and test new analog and digital circuits. There is still much scope for a new EDA tool that can be performed more analysis as compared to the existing ones. However, the use of EDA tools offers a variety of possibilities for designing electronic circuits or chips, although they also have their downsides. In addition to being expensive, many EDA tools are difficult to install on a computer. Almost every EDA tool can be learned easily, and many EDA experts are available to help you achieve proficiency. Even though colleges have excellent tools to use, a lack of skilled instructors means that students aren't learning EDA, but moving into other domains, like software. In the early stages of education regarding EDA tools, if the costs of the EDA tools are kept at a reasonable level, more students can engage in the EDA domain, increasing expertise and accelerating growth in the EDA domain for Accelerating Growth of New India's Innovations.

### **REFERENCES:**

Md. Mydul Islam\*, Faysal Al Mahmud, Md.Haswan Maruf, and Md. Atiqul Islam, (June 2017). Survey on Electronics Design Automation Tools and Software, Dept of Electrical & Electronics Engineering, Green University of Bangladesh, Dhaka, Bangladesh. SEU Journal of Science and Engineering, Vol. 11, No.1

Poonam Dang, Harshal Arolkar, (Mar 2019). Electronic Design Automation Tool: a Comparative Study" International Journal for Research in Applied Science & Engineering Technology (IJRASET) Volume 7, Issue III.

T. Bhanu Praksah Reddy, (Aug 2019). Role of Electronic Design Automation in Circuit Design, Velagapudi Ramakrishna Siddhartha Engineering College, Vijaywada. Vol 6 Issue 3. ISSN: 2349-6002

Pinhong Chen, Desmond A. Kirkpatrick, Kurt Keutzer , (Feb 2001). Scripting for EDA Tools: A Case Study, Conference Paper, IEEE explore. INSPEC Accession Number: 6971045, DOI: 10.1109/ISQED.2001.915211

Fritzing Simulator and Layout Tool, (September 2021). Online Source tool, Retrieved from https://fritzing.org/learning/tutorials/building-circuit

Legal Advantage Blog, (April 24, 2017). EDA Tools. Retrieved from Online Source: https://www.legaladvantage.net/blog/eda-tools/

Max plus II compiler and simulator Tool, (2020). Retrieved from: https://max-plus-ii-baseline.software.informer.com/10.2/

S. Hassoun and T. Sasao, (2002). Logic Synthesis and Verification, Boston, MA, Kluwer Academic Publishers, 454 p.

W. Shum and J. H. Anderson, (Feb 2012). Analyzing and predicting the impact of CAD algorithm noise on FPGA speed performance and power, in Proceedings of the ACM/SIGDA international symposium on Field Programmable Gate Arrays (FPGA'12), pp. 107-110.

Dewey, A. (2000). Digital & Analog Electronic Design Automation, The electrical engineering handbook, CRC Press LLC, 2000.

Petr Fišer, Jan Schmidt, Jiří Balcárek, Faculty of Information Technology, Czech Technical University in Prague, (April 2014). Sources of bias in EDA tools and its influence, Prague, Czech Republic, Conference Paper. ResearchGate, DOI: 10.1109/DDECS.2014.6868803

Luciano Lavagno, Politecnico di Torino, Torino, Italy, Igor L. Markov, University of Michigan, Ann Arbor, Michigan, USA, Grant Martin, Cadence Design Systems, Inc, (Feb 2016). Electronic Design Automation for IC Implementation, Circuit Design, and Process Technology. San Jose, California, USA, Louis K. Scheffer, Howard Hughes, Medical Institute, Ashburn, Virginia, USA. Version Date: 20160224. International Standard Book Number-13: 978-1-4822-5461-7.